An introduction to the EDA space

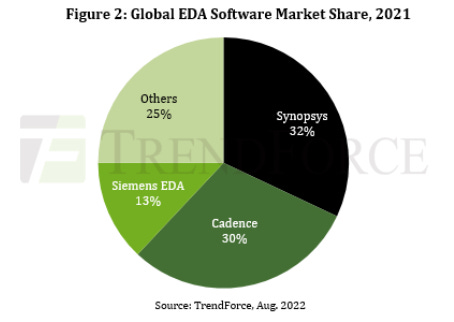

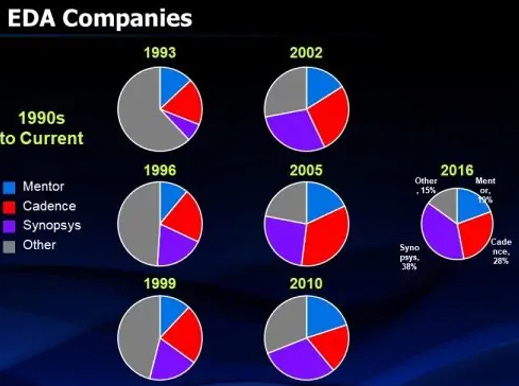

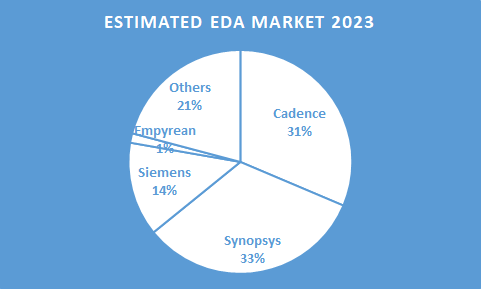

Both Cadence and Synopsys are active in electronic design automation (EDA) software, which is used to design and analyze integrated circuits (ICs) and printed circuit boards (PCBs). This should be an attractive industry for long term investors as the top three vendors — Synopsys, Cadence and Siemens — control around 75% of the market. There is not any real risk of new competitors entering at the moment, even in the Chinese market — where the drive will be substantial to transition to homegrown technologies — the leading player only has a 1% market share currently.

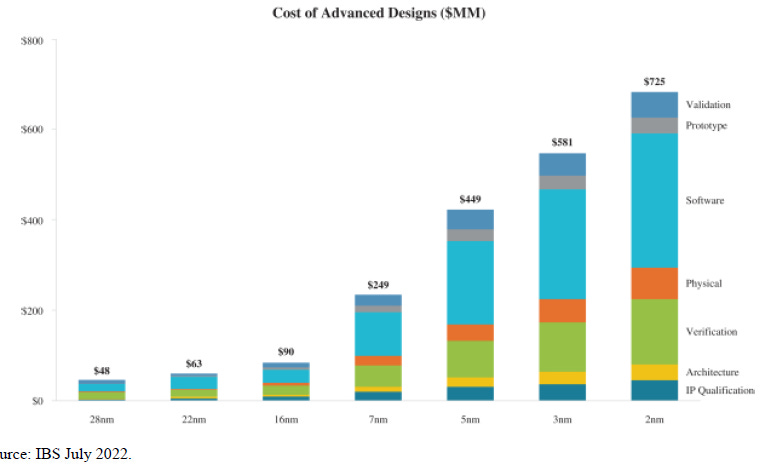

The great thing about software businesses is that revenues are largely recurring via subscription models, so investors already know beforehand how much cash will be coming in as opposed to hardware businesses such as semiconductors which can be notoriously cyclical. On top of that, pricing power is strong as clients don’t tend to switch software providers. You would have to retrain your engineering force on new software which will take months. As the costs of semi design are already getting out of control, e.g. with the design of a state of the art chip costing nearly $1 billion, naturally the semi designer sticks with the best software.

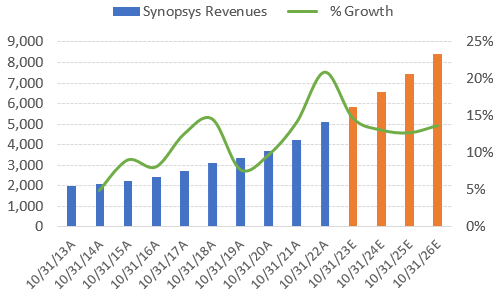

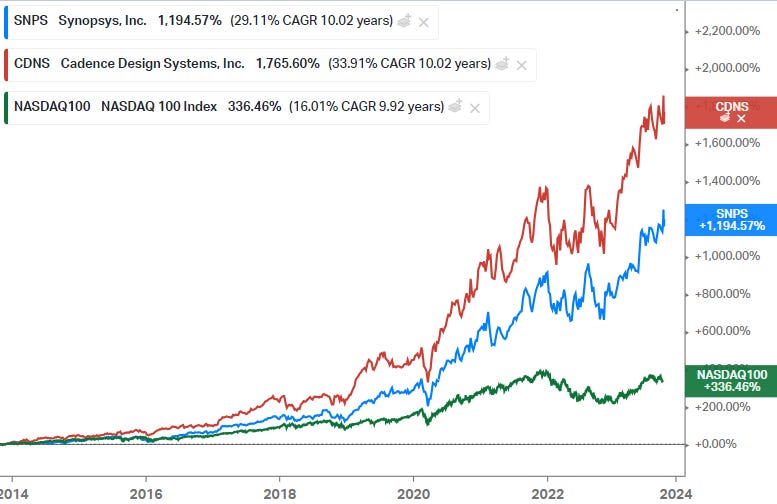

This has resulted in attractive revenue growth for both Cadence and Synopsys:

Growth picked as design costs at the leading nodes increased, with more transistor counts requiring a larger team of design engineers as well as more software to run for example an increasing amount of simulations to verify the chip design.

Arm provides the following estimates for the rise in semi design costs on the leading nodes:

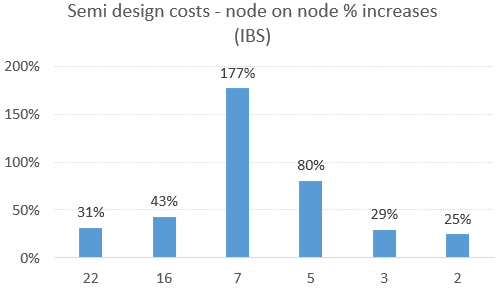

Percentage-wise the biggest jumps occurred at 7 and 5nm with the introduction of EUV (initially quadruple DUV patterning as EUV wasn’t ready). According to the data, these increases would moderate on 3 and 2nm:

If this analysis from IBS is correct, large tailwinds which the EDA companies have been enjoying would start moderating, which could give a drop in top line growth rates. However, long term growth rates should remain attractive nevertheless, as EDA revenues are correlated with semi R&D spend, which in turn is correlated to how many transistors are going into a single chip. On the latter, we have a clear roadmap for the number of transistors within a single die to keep increasing for more than a decade, with both the move to both GAA and CFET type transistors (illustrated by Imec below).

Another trend which will benefit the EDA players is custom silicon, with large companies such as Apple, Amazon, Google, Microsoft and Tesla increasingly in favor of designing their own chips. This means their in-house design teams will need more EDA software as well.

Currently hyperscalers are working with specialist semi designers such as Broadcom and Marvell to develop these specialized custom chips, however, Cadence’s CEO view is that long term they’ll likely take this fully in-house: “The cloud companies, they’re all working very closely with the 2 or 3 main ASIC companies because what happens is when the big system companies do silicon design, they don’t do all of it in-house immediately. They will do the front-end in-house and then do the back-end with an ASIC company. And then later on, they can move the whole thing in-house.”

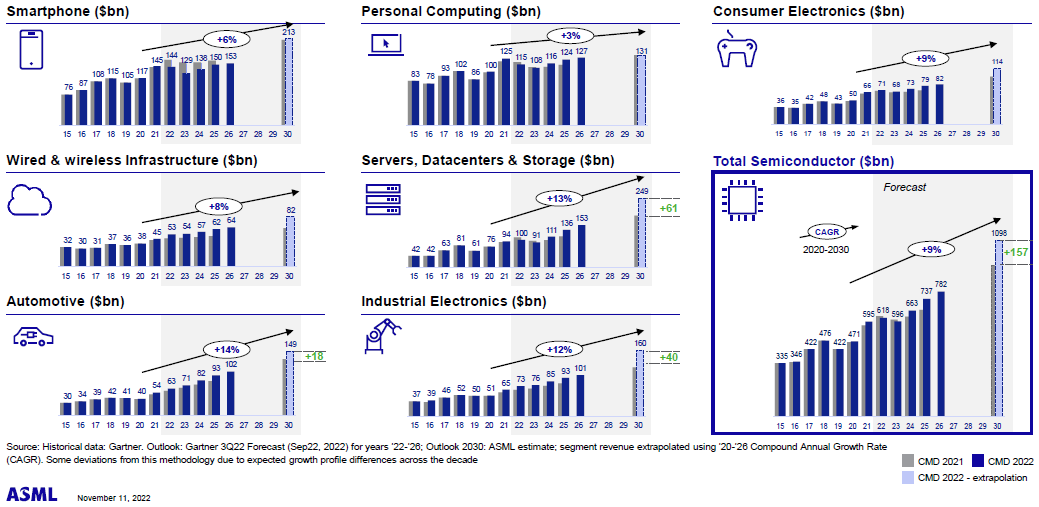

An additional trend in favor of the EDA industry is that semiconductors are seeing increasing applications in a wider variety of end markets, such as automotive, industrials, and AI datacenters. Chips need to be tailored for these specific end markets, which again bodes well for EDA demand.

And as already mentioned, pricing power in the industry is strong, which means that we should see regular price increases above the rates of inflation.

The below chart nicely illustrates where EDA sits in the semi value chain. Taking out the IP part from the number below, the overall EDA market is around 1.5% of the size of the semiconductor market. If around 15% of the semiconductor market is spend on R&D, this means EDA software is around 10% of the R&D budget. A bit further up we’ll go through why this number is likely to increase.

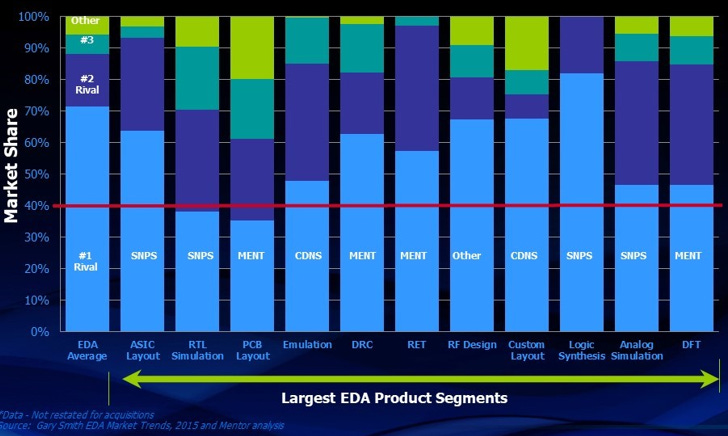

This broader EDA market can be further segmented by the type of semiconductor and the type of workload, where there usually is one software tool which is dominating with a market share of 40% of above. Historically, Cadence was the strong player in analog and Synopsys in digital, but both players now provide a broad portfolio of tools. As the design flow of a chip takes up a series of tools, typically both Synopsys and Cadence have all the top semi designers as their customers, with their customers typically selecting the best of breed tool for each particular task. Siemens acquired the pioneering Mentor Graphics business in 2017, which has now been rebranded under the Siemens brand.

Most of semi design happens in a textual programming language while letting the software tools optimize the chip’s physical design based on these instructions. It is therefore clearly mathematics-heavy software. Connecting trillions of transistors by hand is obviously not feasible, no matter how large your engineering team is.

A simple example of how you can code an inverter in VHDL, a hardware description language used in EDA, is shown below:

During and after the design, regular rounds of simulations will be ran to find bugs. When the chip design is nearing completion, the chip can also be emulated on physical hardware so that accompanying software can be tested on top of it. This way, you can also further develop your hard- and software in parallel while testing both on each other. Large companies such as Nvidia can also provide the emulation hardware of their latest GPUs to large clients, so that those can already start testing the GPUs while building additional software on top. Similarly, the automotive sector is increasingly relying on emulation to start testing their self-driving software on chips still in development. At the end of the design process, when the chip designer is confident that all is working well, he can send the blueprints to TSMC for a tapeout, which can be pricey. If all goes well again, the actual first silicon can then be fabricated and tested, after which the designer can start handing out samples of the product to clients.

The big three players have now been dominating the EDA industry for a few decades. Over the years, both Synopsys and Cadence have been cobbling up smaller niche players in the industry to build up a complete portfolio of software tools, aimed at automating the entire chip design workflow.

AI as the next driver

So, IBS is saying that design cost increases would start moderating from here, which would be a negative for EDA. However, what got me enthused again on the space is that with the use of AI, EDA can become a larger part of semi R&D spend, also while addressing the current shortage in semi engineers. Cadence’s CEO detailed this at the Bernstein conference:

“So EDA for 30 years has been very complicated software but one thing we never did was workflow automation. So EDS software has always been what I would call single run, you give it an input and it gives the output. Say, I want this kind of CPU, it will run for 1 or 2 days typically and do all kinds of optimization and geometric processing. If you go to all big customers of ours, they typically will run Innovus, which is one of the flagship implementation tools. They’ll change something, and they will run it again. Either the process or the design spec changes, or they are exploring the design space for the best power or performance. So what we can do with reinforcement learning, and we have several tools, but one of the tools in implementation is called Cerebrus. It automates that running of searching the design space. So it’s huge value because you’re replacing something that was manual before. What used to take 2 days in one run, if you run it on ten machines in parallel with reinforcement learning, it takes about one week, but 200 runs. So you are replacing like months of work. But what is even more powerful is that the results can be better than achieved by humans, because it’s very difficult to optimize on 17 dimensions. In a lot of cases, we have 5 to 10% better PPA (power, performance and area) than the old way of doing it. So there is a lot of opportunity to capture a bigger percentage of R&D spend. We now have 10 out of the top 20 customers and five big hyperscalers using it. Today, we have 100 billion transistors, by end of the decade, it will be 1 trillion transistors. So the size is going up by 10x but the amount of work is probably going up by 30 to 40x. There is no way to hire 30 to 40 times more engineers. There are not even that many graduating. So what I expect will happen is that the customers will still hire more engineers, maybe like 2 to 3 times more than now but for the rest of the productivity gap, there is an opportunity for a bigger portion of R&D to go to automation.”

Having the amount of work required to design a leading edge chip go up by 30 to 40 times and the amount of work carried out by the EDA software go up 10x is obviously interesting. Especially as the business model is shifting towards billing based on workloads. Cadence’s CEO explaining this:

“EDA is almost all subscriptions, on the emulation hardware, there is some upfront component. Now, some customers will lease the hardware, so it’s subscription, but some big customers will buy it. Overall, our revenue is about 85 to 90% subscription which is great these days. And with a 99% renewal rate or more. Unless the company goes out of business, they will typically renew. And then we have different business models, some products are tied to the number of engineers, but more and more it’s tied to the amount of work that is happening.”

Synopsys’ CFO added some details how the semi designers are using AI tools and how the company is thinking about monetizing these, from the Bank of America conference: “And our first tool is DSO.ai, that’s design space optimization. So the way we monetize it, is you buy our underlying subscription and then you buy the DSO.ai tool per project. And what we’re finding with customers is as they’re running multiple iterations to optimize the design, they actually use more of the underlying tools because they only have a certain amount of time. And so if they have more tools from us, they can run more iterations. What we also announced at the end of March is that we’re launching TSO.ai (for testing) and VSO.ai (for verification). So we’re building AI tools out across the entire design flow. We’re really focused on making sure that we’re driving broad adoption so we can have successful use cases and we’ll experiment over time with additional monetization. It’s one of the reasons that we’re growing faster than the underlying R&D spend.”

Nvidia recently announced that they will be shifting from a two year to a one year cadence in the release of new datacenter GPUs. Clever usage of new AI tools is probably playing a role here, with both Cadence and Synopsys executives commenting that AI tools are being used to accelerate the optimization of the design space. The good news for EDA players is that this should also allow Nvidia’s competitors to move to a faster cadence compared to previously.

Overall, my impression is that these novel AI tools: a) are seeing adoption, b) have strong benefits, especially in speeding up R&D as well as in the final product’s PPA, and c) pricing can be done based on workloads which allows for these benefits to be partly monetized by the EDA industry. On the Cadence Q3 call, we received an update on these developments with the company’s CEO commenting:

“We are seeing growing momentum for our comprehensive JedAI generative AI platform, with an increasing number of customers achieving exceptional quality of results and productivity gains. While still in the early stages, sales of our generative AI solutions have nearly tripled in the last year. Last quarter, we referenced our successes with Nvidia and Tesla. This quarter, we are pleased to announce that Broadcom has accelerated the adoption of Cadence Cerebrus across multiple business units, achieving impressive quality of results. In Q3, we pioneered LLM capabilities to chip design successfully by collaborating with Renesas on accelerating functional specification to final chip design. We are very pleased with the accelerating momentum of our flagship Cadence Cerebrus generative AI solution whose transformative results have led to its deployment at all of our top 10 digital customers and in about 300 tape-outs to date. Imagination Technologies uses Cadence Cerebrus and our full digital flow on its latest 5-nanometer GPU design to achieve a 20% reduction in leakage power.

In the ‘90s, it would take 5 years with 500 engineers to design a big chip. And now that takes 6 to 12 months with maybe 50 engineers. So that’s 100x more efficient than 25 years ago. And I think AI can provide the next level of improvement in productivity and risk mitigation. So it should lead to more design activity, especially by the systems companies. If you have 3 years experience doing chip design versus 20 years, with AI, that gap is narrowing. So less experienced engineers can be almost as productive as more experienced engineers.

When our customers are using more AI tools, these use a lot of underlying tools. So when Cerebrus runs for example, which is our AI tool for digital implementation, one of the most difficult tasks in chip design, one run of Cerebrus will typically run on 10 to 20 machines, each of them could have like 32 or 16 CPUs. So they are using a lot of compute. And they’re using a lot of underlying licenses, so it could be like 10 instances of Innovus which Cerebrus is running.”

So Cadence has around 300 customer tape-outs making use of their AI tools, and Synopsys has a similar number. On the Q2 call, the latter mentioned 270 tape-outs so far with 9 out of the top 10 semiconductor vendors using their AI in production. The CEO also mentioned the following stats on the call: “In the last quarter, our customers have demonstrated up to 10x faster turnaround time and double-digit improvements in verification coverage. Customers are also reporting more than 20% test cost reductions. Synopsys.ai revenue is just starting to ramp, but early proof points give us high confidence in its long-term growth prospects. We’ve moved from project-based experimentations to customers now adding Synopsys.ai subscription.”

So clearly pricing models are still evolving. Given this is largely a two player market, competition on pricing shouldn’t be a factor, and both players should be able to work out how to optimally price for the benefits they’re bringing to the semi industry.

AI driving a transition from best-of-breed to best-of-suite?

In software, there has been a constant battle between best-of-breed, i.e. purchasing the best point solutions from different vendors, and best-of-suite, where you go for the entire software portfolio from one vendor. A good example for best-of-suite is Microsoft Office, as there were better text editors available, e.g. WordPerfect during the eighties, but companies just started buying the Microsoft Office bundle as from the nineties because it was good enough and practical. In EDA, up to now semi designers have been taking the best of breed approach, stringing together the best solutions from different vendors. Synopsys’ founder gave a hint at the JP Morgan conference that this could change:

“We have been fortunate to invest nearly 7 years ago in a fundamental push on AI in the design of chips. And the results have truly been fantastic, meaning that on entire design flows, we’ve been able to reduce the time of design from literally months to weeks. While at the same time improving the quality of results, meaning how fast the chip is, how low power it is, how small can you make it. And at the very moment when there’s a sharp shortage of designers in the world, being able to drive productivity forward substantially is of very high value. There’s one difference between the AI that you see now frequently in the press, sort of the generative AI, and ours. And that one difference is that with generative AI, you get fantastic context and ideas, but maybe everything is not completely correct. We have no such freedom, there can be only zero mistakes. A single transistor doesn’t work, and a whole system can fail. And so the way we have approached this is to make sure that all of our tools are working well together, and the AI is sitting on top of that literally as a governor to run the tools and get better results. This is still at the beginning, and yet we see a very rapid adoption. And going to manufacturing is a very big decision for companies because if they fail, it costs them many millions of dollars. Normally they want to test out things for many years before they use them in production. In this case, the value proposition is so great,and so much of the testing is built into what we do, that the adoption is very fast.”

So the comments here on AI orchestrating a flow of different tools is an interesting one, and similar comments were made on the Cadence call: “Our AI tools will run on the full flow by nature, whether that’s digital implementation or verification.” As both Cadence’s and Synopsys’ AI is only operating on their tools, this might lead to a hard decision for customers which portfolio of tools they will take for one particular workflow. Synopsys’ founder added some further details here:

“This time, it’s not an individual tool doing a step better, it is a whole set of tools that have been harnessed together. We call it fusion, meaning they work really well together and they share information. And this was an AI pioneering step of being able to get quality results that were better than what the traditional design flow with the best tools in hand could achieve by quite a number of percentage points in both speed and power. And so not only can we move these steps from months to weeks, we also do that with one or two engineers versus a dozen or so, including many specialists.”

Player 1, Cadence

Cadence offers a portfolio of software products covering everything from designing digital and analog semis to printed circuit boards (PCBs), as well as tools for optimizing the design, debugging and verification. Their new AI platform, JedAI, is interwoven into these tools. For example in the software tool Verisium, which is used for debugging and verification, the AI will detect where bugs are coming from.

The company was founded in 1987 and its software portfolio has been expanding by both M&A and internal development over the decades. A few examples of acquisitions include:

1989 - the acquisition of Gateway Design Automation, the leading supplier of logic simulation technology.

1991 - the merger with Valid Logic Systems, a leader in printed circuit board design tools.

2005 - the acquisition of Verisity, a provider of automated verification software.

An example of some of the simulations which can be ran on Cadence’ software highlighted below. You can thermally simulate for example how much heat the different parts of a chip will generate, and do the same for the entire package, the PCB, the server rack, and the entire datacenter.

One of the big trends in semiconductors over the coming decade is going to be 2.5D and 3D packaging, where a variety of dies are packaged closely together, making them operate as one unit. Cadence’s CEO detailed the company’s strength in this area:

“So the way to increase the size of the chip is 3D-IC. If you look at the last 5 years, performance has come for putting more things on the chip. So instead of one CPU, now there are 8 CPUs, Amazon’s Graviton has 7 chiplets on an interposer, and that’s starting in high-performance computing at first, but I think it will permeate. In 3D-IC, the most important part is package design. So we have a majority share in package design software, it’s called Allegro. So we can put a system together with chip and package design software and then run thermal dissipation analysis on top, which is one of the biggest issues in 3D-IC. Cadence is the only company to have this platform. TSMC launched 3Dblox in October, and a lot of it is based on this Cadence flow.”

The company sees themselves as a provider of mathematical software, and they recently acquired OpenEye in quite a different field than the traditional semiconductor arena. OpenEye is a molecular design and simulation software used in drug development and the company mentions it has 19 out of the top 20 pharmaceutical companies as its customers. So overall it looks to be a quality asset. Cadence’s CEO sees OpenEye leveraging from Cadence’s skills in AI, simulation software and specialized hardware. He explained this on the Q3 call:

“We are super excited about molecular design and its future. It’s almost like where EDA was 20 years ago. So the reason we acquired OpenEye, is physics-based biological simulation. There are very few companies that can do that. But then we can add to it AI-based drug discovery and computational hardware. OpenEye has a cloud-based platform, Orion, and recently we expanded our collaboration with a major top 5 pharmaceutical company to do traditional and AI-based drug discovery on top of Orion.”

Cadence segments its business into functional verification, digital IC, custom IC, system design, and semiconductor IP. System design is a computer aided design (CAD) software focused on electronic products embedding chips, such as an Apple iPhone for example. When it comes to IP — which you can sort of see as lego blocks which you can use in your chip design, i.e. a particular IP block will bring certain functionalities for the chip so you don’t have to design those yourself — Synopsys has a much bigger portfolio here so we’ll go through this industry in the subsequent section. In the meanwhile, Cadence’s CEO explained why their IP portfolio is much more limited: “IP, this is good business, but it’s not as profitable as EDA because the customer always can build versus buy, i.e. he can design it himself or buy it. Whereas in EDA, there’s no way even for the biggest companies in the world to do their own. So EDA is always better margin. We do critical IP like 3D-IC, UCI interface or DDR.”

The company is diversified geographically with also China contributing 18%. Cadence mentioned that they’re dealing with piracy issues in the Chinese market so if this could get resolved, that would provide a revenue uptick. A risk however here could be further export restrictions, which we’ll touch on in a bit.

Player 2, Synopsys

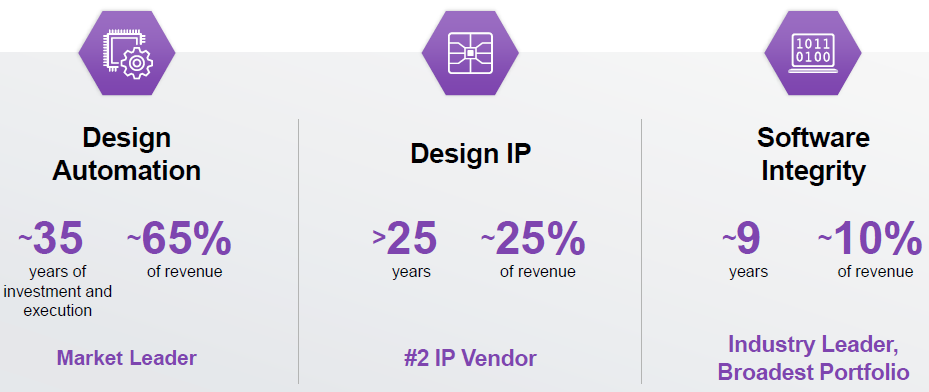

As already mentioned, Synopsys has a larger IP portfolio than Cadence, contributing 25% to revenues. The bread-and-butter of the business remains design automation contributing 65%. The company also has a software integrity business, which handles code verification for programming. An example of the latter is making sure that no malware has been introduced in a codebase.

In its simulation software, Synopsys has especially been investing in chiplet technology (2.5D packaging). Synopsys’ founder explaining this: “You’re all familiar of course with Moore’s Law, this notion of smaller transistors and more of them, but you have also heard maybe that it’s slowing down. There’s an alternative that is just now starting to open up, which is the notion of taking big chips, breaking them into smaller ones, and bringing them very closely together. This is sometimes called multi-die or chiplets. The challenge of that is when you take multiple chips and try to bring them very closely together, it’s all about the speed and the amount of energy in communication, and these are difficult problems. But challenges are opportunities, and so we are in the midst of that because Synopsys has invested in the lowest level of verification and simulation at the atomic level for chips.”

Synopsys’ CEO discussing their AI exposure on the Q2 call: “Synopsys is the leading EDA provider to AI chip designers. Designers are requiring unmatched capabilities in design tools, particularly at the most advanced nodes. They also need our leading interface IP portfolio as AI chips are banking on enormous amounts of data, driving new, faster and lower power interconnect, Synopsys excels at this. In summary, AI chips are a core value stream for Synopsys, already accounting on a trailing 12-month basis for well over USD 0.5 billion and we see this growth continuing throughout the decade.” This revenue stream from AI is roughly 10% of revenues.

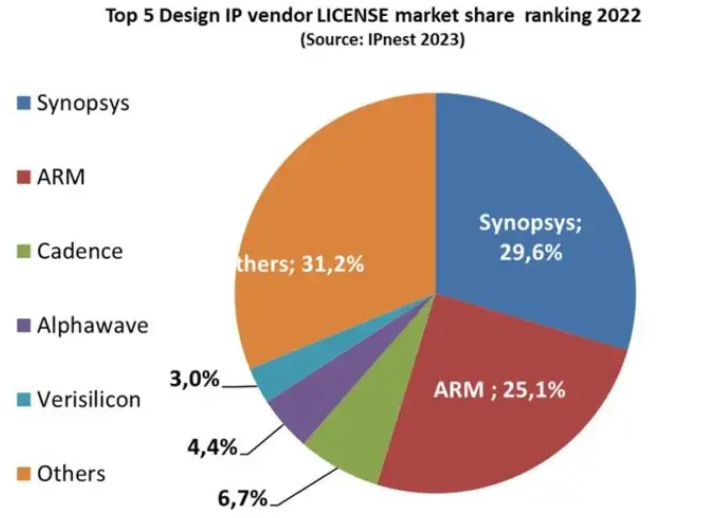

According to IPnest’s data, Synopsys has now overtaken ARM as the number one IP provider globally in terms of licenses sold. IP licensing is basically the selling of blueprints, how parts of a chip can be designed so that the customer doesn’t have to design an entire chip from scratch. So a designer can buy for example an IP block that will handle the communication with other computing units, so that he can focus on customizing the other parts of the chip where he wants to add differentiation.

IP also has to be continuously updated for each new technology node, so when Intel introduces their Intel 3, 2 or 18A nodes, blueprints will have to be specifically designed for these nodes. This is very costly, so this business has reasonable barriers to entry.

Like the EDA software business, IP has been built-up by acquisition over the years. Recently Synopsys for example added some interconnection IP from Rambus to their portfolio.

The nice part of this business is that once the licenses are sold, Synopsys will accumulate royalties over subsequent years, as long as the customer’s chips are being sold. ARM is still the dominant leader in the royalties market with a 64% market share, due to the large amount of licenses they’ve sold over the previous decades and which are still bringing in revenues.

Overall, I’m seeing IP as a good business. So I like Synopsys’ large portfolio here. Synopsys’ CEO also mentions that it expands their customer relationships, giving them sticky connections directly into the semi design teams. The company sees this business growing mid-teens per annum, so obviously, that’s an attractive growth rate.

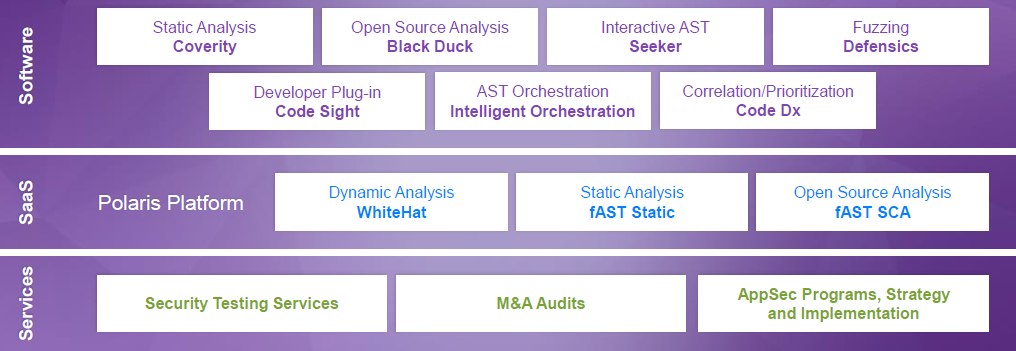

Similar to Cadence’s molecular software business, Synopsys has an odd duck in their portfolio as well with the software integrity business. As already mentioned, this software does all sorts of checks on code written by a customer’s programmers. So it is really a traditional software business being marketed in very diverse end-markets, ranging from financials to health care. Synopsys’ founder detailed how they got into this business:

“Software integrity, we got into that because in the mid-2000s, I had observed that even in semiconductor companies more than half of the engineers were software engineers. And with that comes a quick conclusion which is, a, some of the value is created in software rather than hardware; and b, software design was much less disciplined than hardware development. So we decided to invest in the quality of software and then somewhat unexpectedly, maybe in the early 2010s, we came to realize that the security is just as important as the safety. Initially, we were very much in the space that was between hardware and software, so embedded software. But today, a large portion of our business comes from a broad set of companies that as an EDA company, we would never have talked to, like an oil company, financial companies, health companies and so on.”

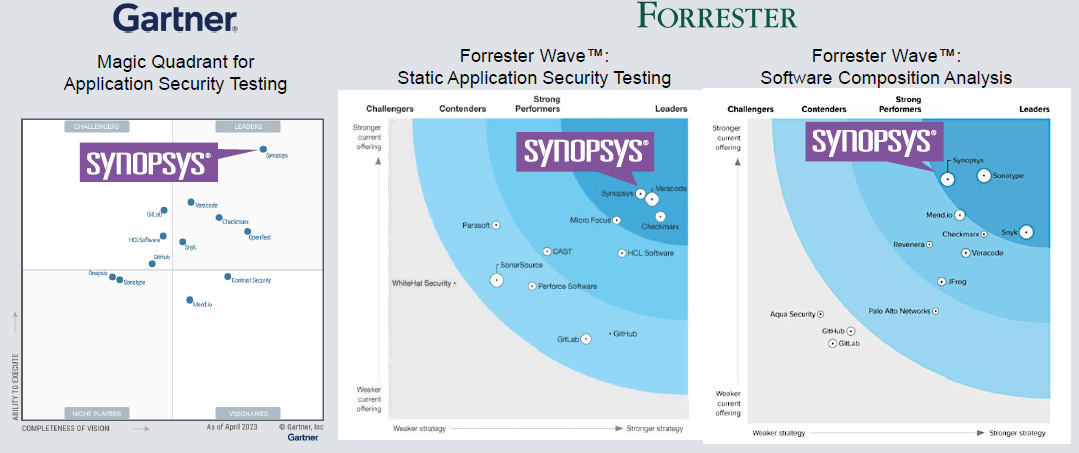

It looks to be a quality asset as the business is doing around USD 500 million in revenues, with the company having a market share of around 20 to 25%. So Synopsys will obviously be a leading player in this market which is also confirmed by Gartner and Forrester (charts below). Additionally, the business is seeing high growth rates, with the company projecting the unit to continue growing at around 15 to 20% per annum.

An overview of the company’s capabilities in software integrity:

That said, this software business could probably be better managed by a traditional software company. It would probably fit in well with Microsoft’s Github or Nasdaq-listed Gitlab for example. However, as it looks to be a decent business, I’m not complaining about it being there.

Chinese export sanctions & local competition

The first export sanctions to China imposed by the US came in 2019, when Huawei was fully cut off from US technology including EDA software. Last year, we had the second round of sanctions, this time targeted at advanced technology. While both Cadence and Synopsys commented that the current impact of these is very limited for them, naturally the potential threat of further sanctions is a risk. Obviously this would be a big negative as 18% of Cadence’s revenues are coming from China and 16% for Synopsys.

And given what has happened to Huawei, no doubt that this will spur large amounts of Chinese investments to build homegrown EDA tools. However, Empyrean Technology is the largest Chinese domestic EDA vendor and they are still at a very small scale compared to Cadence and Synopsys. Looking at their projected revenues for this year, I calculate the below market share data for the 2023 EDA market, giving Empyrean a 1% market share.

Cadence’s CEO discussed these topics at the Wells Fargo conference: “If you look at the last 5 years, our China business is growing like a 20%-plus CAGR. So I expect China to be a good business long term. There are two kinds of questions we get. One is on local development in China, there are some companies trying to write EDA tools. And second is US regulation. The US regulation is a long topic, but in summary, the impact to Cadence is pretty limited. I mean, those regulations are targeted mostly towards manufacturing in China at this point. And even if you go to China, all the big companies are not manufacturing in China, they are manufacturing in TSMC or Samsung. So we are more connected to the design activity. So now the second part is, will there be local competition in China? Because at this point, we are in a very strong position. So these things take a long time. There are some very small companies doing point tools. But to really do a full flow at 3-nanometer, of course we watch it very carefully, but I’m not concerned that this is a short to midterm issue with local competition in China. So overall, I’m pretty optimistic about the China market, yes.”

Financials

Both Cadence and Synopsys have been stellar performers over the last decade, easily outperforming the NASDAQ index:

However, looking at both companies’ valuation compared to a basket of quality tech, well, they make other expensive names such as Microsoft and Airbnb look cheap, and that isn’t easy. On the positive, I do believe that AI can become a meaningful revenue driver over the coming decade, as well as with the attractive trends in custom silicon, advanced semis driving automation in a wide variety of sectors in the economy, and both companies’ strong pricing power. So both Cadence and Synopsys could be looking at a long runway of double digit revenue growth, translating into much higher EPS growth.

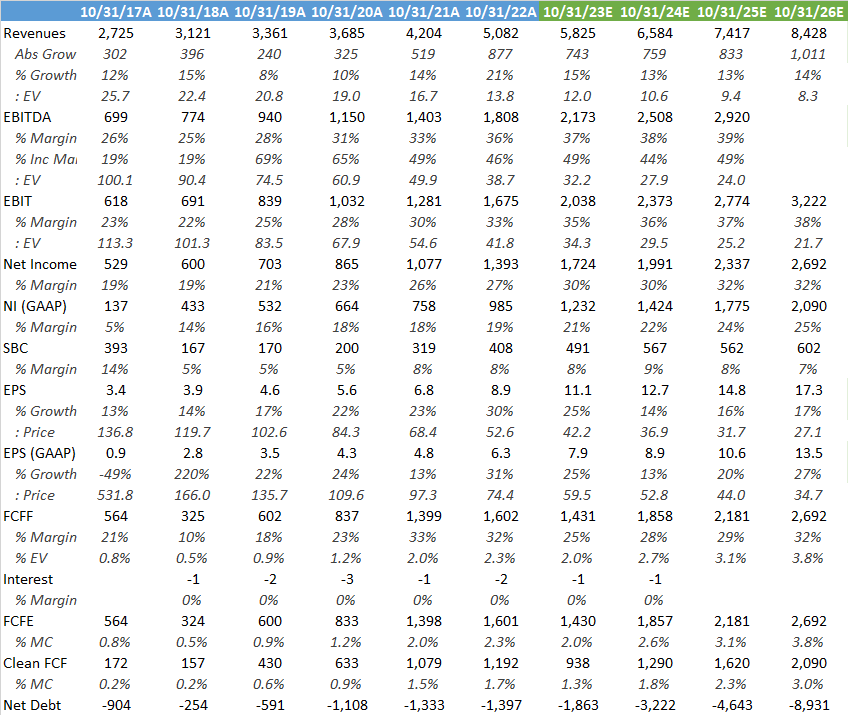

Wall Street’s estimates for Synopsys below, with analysts forecasting double-digit top line growth rates combined with margin expansion. Putting 2026 EPS numbers on around 35x, you can still make an IRR of above 15%.

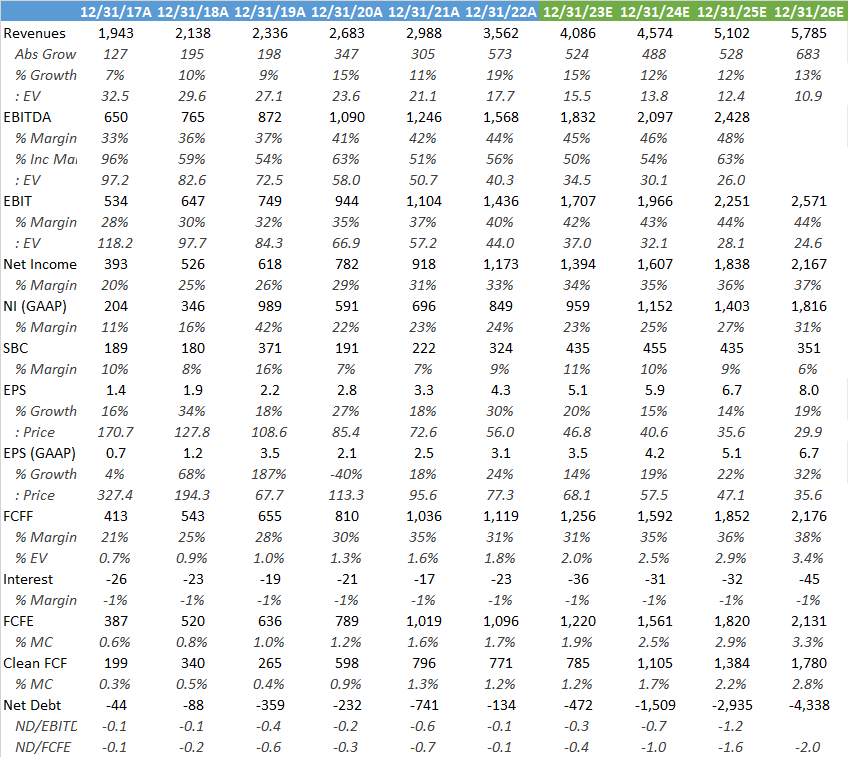

A similar analysis can be made for Cadence, on a multiple of around 35x 2026 EPS, one could still make a double-digit annualized return.

Synopsys’ historical revenue and EPS chart:

Same for Cadence:

Overall, both names should be of interest to long term investors, these are some of the best quality names in the tech sector given the limited competition and clear revenue opportunities.

If you enjoy research like this, hit the like button and subscribe. Also, please share a link to this post on social media or with colleagues with a positive comment, it will help the publication to grow. All shares are appreciated.

I’m also regularly discussing tech and investments on my Twitter.

Disclaimer - This article is not a recommendation to buy or sell the mentioned securities, it is purely for informational purposes. While I’ve aimed to use accurate and reliable information in writing this, it can not be guaranteed that all information used is of this nature. The views expressed in this article may change over time without giving notice. The future performance of the mentioned securities remains uncertain, with both upside as well as downside scenarios possible. Before investing, I recommend speaking to a financial advisor who can take into account your personal risk profile.

Pinning this for later! Been watching these two for a while now but never quite find the brain capacity to learn them. Thanks for your work!

thanks so much for this analysis. I'm a journalist and I'm trying to get my head around the implications of Synopsys' planned Ansys acquisition. Any way we could speak? I'd be very grateful for your insights.